# Peripheral Component Interconnect (PCI) bus implementation in HP ProLiant servers

technology brief

| Abstract                       | 2 |

|--------------------------------|---|

| ntroduction                    | 2 |

| PCI revisions                  | 2 |

| PCI interface                  | 3 |

| HP ProLiant server PCI support | 4 |

| Getting the most out of PCI    |   |

| Conclusion                     | 6 |

| For more information           | 7 |

| Call to action                 | 7 |

## Abstract

The Peripheral Component Interconnect (PCI) bus found in PC, workstation, and server products has evolved over time to keep pace with advances in microprocessor and networking technology. This brief explains how the evolution of the PCI specification from PCI to PCI-X has affected compatibility of existing PCI adapters and PCI slots. This brief also explains why customers migrating to the latest generation of HP ProLiant servers may find it cost effective to update some legacy I/O adapters.

#### Introduction

The PCI Special Interest Group (PCI-SIG) developed the PCI bus specification to overcome impending bottlenecks with existing interfaces such as the EISA bus, the most widely used I/O interface at the time. Introduced in 1992 as a 32-bit, 33-MHz interface, the initial PCI bus offered three times the prevalent EISA bandwidth. The PCI-SIG, of which HP is a contributing member, continues to control and enhance the PCI bus specification to keep pace with evolving microprocessor and networking technology. The latest revisions to the PCI bus allow even higher speeds for increased I/O performance that can complement today's and tomorrow's processor speeds.

## PCI revisions

Table 1 shows the PCI bus revision history. All revisions are backward compatible, meaning that a system designed to meet PCI-X specification version 2.0 can support PCI cards built to earlier PCI-X and PCI revisions, although some restrictions (discussed later in this document) may apply.

| Specification<br>revision | Year<br>introduced | Clock                        | Signaling level supported by slot | Peak bandwidth                                                                                                                       |

|---------------------------|--------------------|------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| PCI 1.0                   | 1992               | 33 MHz                       | No slots defined                  | 133 MB/s @ 32 bits, 266 MB/s @<br>64 bits                                                                                            |

| PCI 2.0                   | 1993               | 33 MHz                       | 5 or 3.3 V                        | 133 MB/s @ 32 bits, 266 MB/s @<br>64 bits                                                                                            |

| PCI 2.1                   | 1995               | 33 MHz<br>66 MHz             | 5 or 3.3 V<br>3.3 V               | 133 MB/s @ 32 bits, 266 MB/s @<br>64 bits<br>266 MB/s @ 32 bits, 533 MB/s @<br>64 bits                                               |

| PCI 2.2                   | 1998               | 33 MHz<br>66 MHz             | 5 or 3.3 V<br>3.3 V               | 133 MB/s @ 32 bits, 266 MB/s @<br>64 bits<br>266 MB/s @ 32 bits, 533 MB/s @<br>64 bits                                               |

| PCI 2.3                   | 2002               | 33 MHz<br>66 MHz             | 5 or 3.3 V<br>3.3 V               | 133 MB/s @ 32 bits, 266 MB/s @<br>64 bits<br>266 MB/s @ 32 bits, 533 MB/s @<br>64 bits                                               |

| PCI-X 1.0                 | 1999               | 66 MHz<br>100 MHz<br>133 MHz | 3.3 V<br>3.3 V<br>3.3 V           | 266 MB/s @ 32 bits, 533 MB/s @<br>64 bits<br>400 MB/s @ 32 bits, 800 MB/s @<br>64 bits<br>533 MB/s @ 32 bits, 1.07 GB/s @<br>64 bits |

#### Table 1. PCI revision history

| Specification revision | Year<br>introduced | Clock                                              | Signaling level supported by slot                             | Peak bandwidth                                                                                                                                                                                                                     |

|------------------------|--------------------|----------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI-X 2.0              | 2002               | 66 MHz<br>100 MHz<br>133 MHz<br>266 MHz<br>533 MHz | 3.3 V<br>3.3 V<br>3.3 V<br>3.3 V and 1.5 V<br>3.3 V and 1.5 V | 266 MB/s @ 32 bits, 533 MB/s @<br>64 bits<br>400 MB/s @ 32 bits, 800 MB/s @<br>64 bits<br>533 MB/s @ 32 bits, 1.07 GB/s @<br>64 bits<br>1.07 GB/s @ 32 bits, 2.13 GB/s @<br>64 bits<br>2.13 GB/s @ 32 bits, 4.27 GB/s @<br>64 bits |

#### Note:

The 5-volt/3.3-volt references in this paper refer only to the signaling level and not to the power that the slot provides to the card.

#### PCI interface

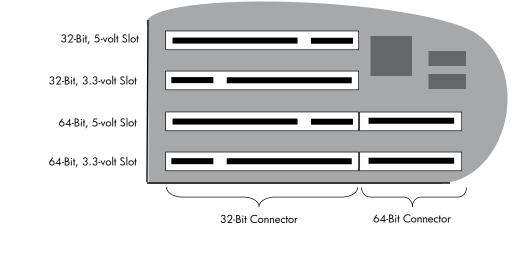

The PCI interface provides two bus widths (32- and 64-bit) and two signaling levels (5- and 3.3-volt). Figure 1 shows the four types of PCI expansion slots used on personal computers and servers.

Figure 1. PCI bus expansion slots (generic system board, top view)

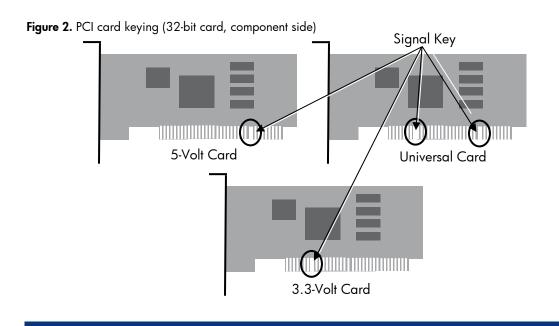

Adapter bus widths and slot bus widths are completely interoperable; a 32-bit card can be used in a 64-bit slot and a 64- bit card can be used in a 32-bit slot (although its operation will be limited to 32-bit transfers). However, the signaling level may restrict where a card can be installed. A keyed scheme is used on the 32-bit connector to determine the signaling level. Correspondingly, PCI cards are keyed in one of three ways: 5-volt, Universal, or 3.3-volt (Figure 2). A Universal card can be installed in either a 5- or 3.3-volt slot, but a 5- or 3.3-volt card must be installed in a slot that specifically supports its level of signaling.

### HP ProLiant server PCI support

The PCI bus has followed the industry trend of moving away from legacy 5-volt signaling toward a smaller voltage swing required by high-speed logic. While 33-MHz PCI operations may use 5- or 3.3-volt signaling, all speeds above 33 megahertz require 3.3-volt (or less) signaling.

The PCI specification allows for cross- and backward-compatibility, but the level of signaling a system supports (as determined by the slot keys) may restrict which cards will work in a given system. The latest systems designed to support faster slots with 3.3-volt signaling will accept only Universal and 3.3-volt PCI cards. Legacy cards keyed for 5-volt signaling will not work in systems that provide only 3.3-volt slots.

As shown in Table 2, the HP ProLiant line includes two models that support legacy (5-volt) PCI cards: the HP ProLiant ML350 G3 and the HP ProLiant DL760 G2 servers.

| ProLiant<br>series | System<br>model | <i>, , , , , , , , , ,</i> |       |

|--------------------|-----------------|----------------------------|-------|

| ML Servers         | ML310           | 64-bit, 33-MHz PCI (4)     | 3.3 V |

|                    | ML330 G3        | 64-bit, 33-MHz PCI (4)     | 3.3 V |

|                    | ML350 G3        | 32-bit, 33-MHz PCI (1)     | 5 V   |

|                    |                 | 64-bit, 100-MHz PCI-X (4)  | 3.3 V |

|                    | ML370 G3        | 64-bit, 100-MHz PCI-X (6)  | 3.3 V |

|                    | ML530 G2        | 64-bit, 100-MHz PCI-X (7)  | 3.3 V |

|                    | ML570 G2        | 64-bit, 100-MHz PCI-X (7)  | 3.3 V |

| DL Servers         | DL320 G2        | 64-bit, 33-MHz PCI (1)     | 3.3 V |

|                    | DL360 G3        | 64-bit, 100-MHz PCI-X (2)  | 3.3 V |

Table 2. ProLiant server PCI slot configurations

| ProLiant<br>series | System<br>model | Slot type (Qty)            | Signal level |

|--------------------|-----------------|----------------------------|--------------|

|                    | DL380 G3        | 64-bit, 100-MHz PCI-X (2)  | 3.3 V        |

|                    |                 | 64-bit, 133-MHz PCI-X (1)  | 3.3 V        |

|                    | DL560           | 64-bit, 100-MHz PCI-X (2)  | 3.3 V        |

|                    |                 | 64-bit, 133-MHz PCI-X (1)  | 3.3 V        |

|                    | DL580 G2        | 64-bit, 100-MHz PCI-X (6)  | 3.3 V        |

|                    | DL740           | 64-bit, 100-MHz PCI-X (6)  | 3.3 V        |

|                    | DL760 G2        | 64-bit, 33-MHz PCI (1)     | 5 V          |

|                    |                 | 64-bit, 100-MHz PCI-X (10) | 3.3 V        |

| BL Servers         | BL10e G2        | No PCI slots               |              |

|                    | BL20p G2        | No PCI slots               |              |

|                    | BL40p           | 64-bit, 100-MHz PCI-X (2)  | 3.3 V        |

### Getting the most out of PCI

While the latest PCI-X-compliant servers are backward compatible with 33-MHz PCI cards, the faster PCI-X cards will better complement the performance of gigahertz processors in those servers. Using 33-MHz PCI cards in a new system, even if they are compatible, may result in a performance penalty that negates the advantage of using a new server.

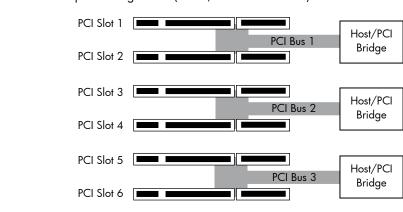

A PCI bus operates at the clock rate of the slowest card installed on that bus. Therefore, for optimum performance, PCI cards of different speeds should not be installed on the same bus.

Select HP ProLiant servers feature multiple PCI buses within a single system unit. A peer arrangement of multiple buses (Figure 3) allows higher I/O throughput by providing multiple parallel paths to main memory.

Figure 3. Multi-PCI bus peer configuration (64-bit, 3.3-V slots shown)

# Conclusion

As microprocessor speeds climb beyond the 3-GHz mark, the performance of peripheral components continues to improve as well.

As a founding member of the PCI-SIG and a leader in the development of the PCI family of specifications, HP is committed to delivering the high performance that ProLiant server applications require and the investment protection that ProLiant customers demand. HP is at the forefront of on-going development within the PCI-SIG of future generations of fully compatible PCI-X speeds and software-compatible PCI Express alternatives. HP's dual commitment to performance and investment protection is the guiding principle behind the development both of these industry standards and the ProLiant products that implement them.

The latest HP ProLiant servers implement PCI–X architecture and are well equipped to handle broadband communications requiring gigabit Ethernet controllers, fiber channel I/O, or cluster interconnects. Systems configured with Ultra320 SCSI drives will also benefit with the latest PCI-X bus support.

Administrators who decide to migrate to the latest generation of HP ProLiant servers need to assess updating any legacy 5-volt I/O adapters as well. While this transition may incur cost, it ensures compatibility with the majority of today's industry-standard servers.

#### For more information

For more information on HP ProLiant servers and solutions, access the HP web site at <a href="http://www.hp.com/servers/proliant">www.hp.com/servers/proliant</a>

For more information on the PCI interface, access the PCI-SIG web site at <u>www.PCISIG.com</u>.

### Call to action

To help us better understand and meet your needs for ISS technology information, please send comments about this paper to: <u>TechCom@HP.com</u>.

© 2003 Hewlett-Packard Development Company, L.P. The information contained herein is subject to change without notice. The only warranties for HP products and services are set forth in the express warranty statements accompanying such products and services. Nothing herein should be construed as constituting an additional warranty. HP shall not be liable for technical or editorial errors or omissions contained herein.

All product names mentioned herein may be trademarks of their respective companies.

TC031106TB, 11/2003